An implementation-defined number of interrupts in the range 1-240 interrupts. Nested Vector Interrupt Controller.

Nested Vectored Interrupt Controller Nvic Arm Cortex M

A higher level corresponds to a lower priority so level 0 is the highest interrupt priority.

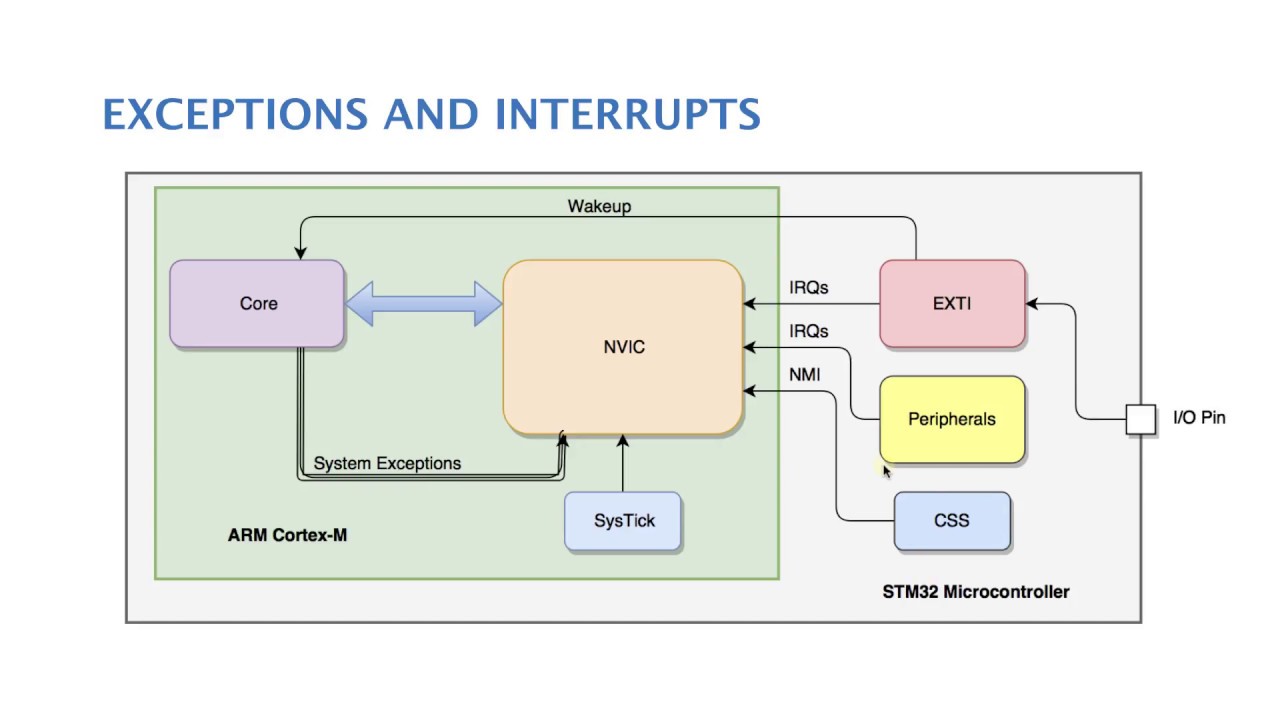

. It is closely coupled to the processor core and provides a number of features as follows. Defferent peripheral can trigger interrupt like data come to USART ADC finished conversion timer overflow and more more. View What is nested vector interrupt control NVIC_pdf from MBE 3058 at City University of Hong Kong.

At the start we will explain the exception and interrupt concepts that are. The main features are. Answer 1 of 4.

Nested Vectored Interrupt Controller. Understanding the STM32 NVIC Nested Vectored Interrupt Controller The NVIC on the STM32 series of ARM Cortex-M micro-controllers is a very powerful tool that can be used to handle any type of interrupt. The interrupt architecture and priorities are very flexible and highly configurable to support RTOS.

So it has 16 programmable priority levels. Nested vectored interrupt controller tutorial An absolute beloved of mine this all black nail art helps make utilization of matte and gloss. Micro-Coded Architecture So that interrupt stacking entry and exit are done automatically in hardware.

Nested Vector Interrupt Controllers or NVIC for short have two properties. Nested Vector Interrupt Controller. NVIC or Nested Vector Interrupt Controller is used to dinamically tell which interrupt is more important and for enabling or disabling interrupts.

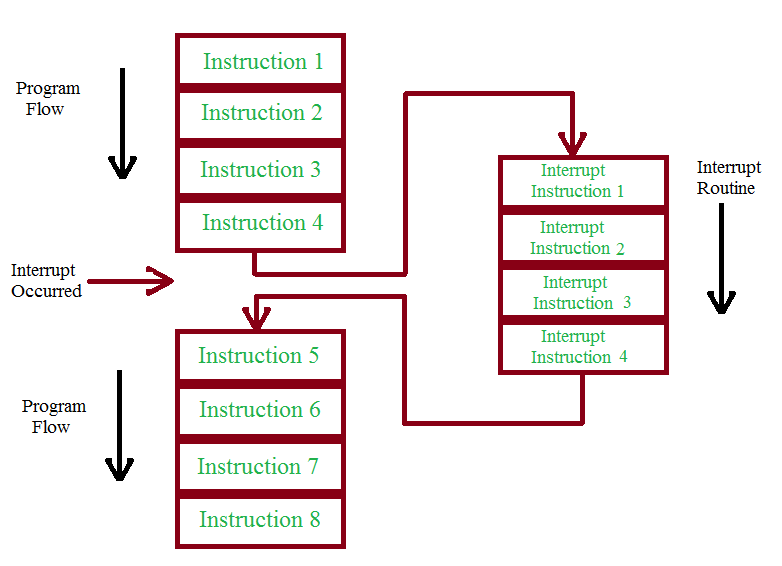

Nested vector interrupt control uses a vector table that contains the addresses of the ISRs for each interrupt. Double click the Vectored Interrupt Controller component to add this component to your SOPC Builder System. Interrupt vector and irq mapping in do_IRQ.

Everything with all black is a complete winner for me. Nested Vectored Interrupt Controller. Vectored Interrupt Controller Component.

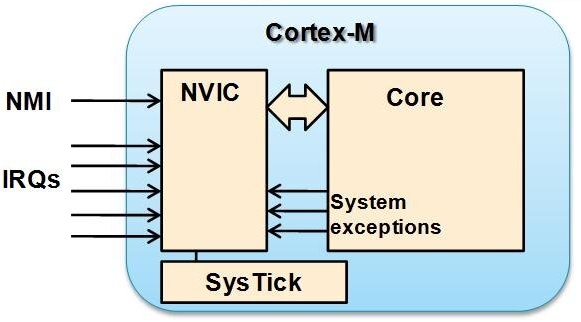

The Cortex-M3 processor includes an interrupt controller called the Nested Vectored Interrupt Controller NVIC. Modified 5 years 6 months ago. Functions to access the Nested Vector Interrupt Controller NVIC.

Nested Vectored Interrupt Controller. Seek to live currently behind live LIVE. Can handle multiple interrupts.

A programmable priority level of 0-255 for each interrupt. Ask Question Asked 5 years 6 months ago. By continuing to use our site you consent to our cookies.

NVIC is an on-chip controller that provides fast and low latency response to interrupt-driven events in ARM Cortex-M MCUs. You can select and configure where applicable each exception using the following control groups. It supports the system exception and interrupt occurrence.

The prioritization and handling schemes of nested vector interrupt control reduce the latency and overhead that interrupts typically introduce and ensure low power. Viewed 3k times. NVIC NVIC or Nested Vector Interrupt Controller is used to dinamically tell which interrupt is more important and.

One of 16 priorities could be assigned to each interrupt source. Theres a thing about black that exudes electrical power and self esteem. Current Time Duration.

The file must be adapted by the silicon vendor to include interrupt vectors for all device-specific interrupt. MARCH 20 2019 BY DANIELLE COLLINS LEAVE A. The number of interrupts implemented is device-dependent.

When an interrupt is triggered the processor gets the address from the vector table. There is an interrupt called each time data arrive to MCU. Hello and welcome to this presentation of the Nested Vector Interrupt Controller or NVIC module for Kinetis K series MCUs.

In this session youll learn about the NVIC its main features and the application benefits of leveraging this function. Remaining Time - 1x. Level and pulse detection of interrupt signals.

Breakpoint inside interrupt C. The interrupt controller belongs to the Cortex-M0 CPU enabling a close coupling with the processor core. This section describes the NVIC and the registers it uses.

A programmable priority level for each interrupt. So heres a tutorial on how to use it The NVIC on the STM32F4 uses 4 bits to define priority levels. Cortex-M0 Nested Vector Interrupt Controller.

A higher level corresponds to a lower priority so level 0 is the highest interrupt priority. Which includes the Nested Vectored Interrupt Controller NVIC. The priority for each interrupt source is programmable four levels.

Selected Interrupt This group shows exception-specific controls. Application could benefit from dy namic prioritization of the. Nios II Processor with EIC Interface Figure 3.

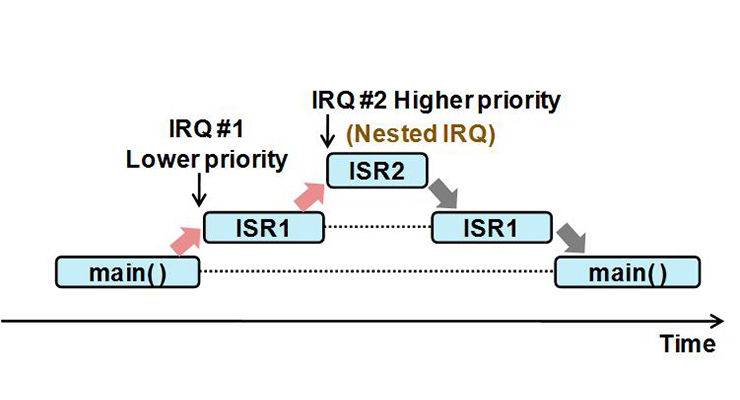

If two pending interrupts share the same priority priority is given. Nested interrupt support Vectored interrupt support Dynamic priority changes support Reduction of interrupt latency Interrupt masking. This site uses cookies to store information on your computer.

Arm provides a template file startup_device for each supported compiler. What is nested vector interrupt control NVIC. The ARM Cortex -M0 Nested Vector Interrupt Controller NVIC provides an interface between interrupt sources external to the core peripherals and external pins and the core.

This section explains how to use interrupts and exceptions and access functions for the Nested Vector Interrupt Controller NVIC. The Nested Vectored Interrupt Controller dialog for Cortex-M0 and Cortex-M0 shows the status of all exceptions. Differences among various interrupts.

Important Information for the Arm website. Nested Vectored Interrupt Controller Tutorial. The NVIC block suspends the calculation processing that is running on the main core and controls switching to prioritized processing.

In a controller we enable every interrupt with certain priority levels and the interrupt is servicedprocessed wrt the priority level. For each exception the dialog shows the number source name state and priority. Servicing processing the interrupt means the processing of line of codes inside the IRQ handler of the respective interrupt.

32 interrupt sources 4 programmable priority levels low-latency exception and interrupt handling Automatic nesting Power management control Applications can benefit from dynamic prioritization of the interrupt levels fast response to the. The Nested Vectored Interrupt Controller embedded inside of the STM32L4 microcontroller provides up to 91 interrupt channels on STM32L49x4A6 devices served with low latency. Parameterization When you add the VIC to your system the Vectored Interrupt Controller MegaWizard interface appears as shown in Figure 4.

Facebook Twitter LinkedIn Printer Video Player is loading. In this tutorial We will explain the role of the nested vectored interrupt controller NVIC in interrupt handling requests of ARM Cortex-M microcontrollers. If a high-priority exception interrupt is required during exception processing then the NVIC block.

Which offloads this work overhead from the CPU. It supports up to 256 different interrupt vectors. Defferent peripheral can trigger interrupt like data come to USART ADC finished conversion timer overflow and more more.

Nested Vectored Interrupt Controller Nvic Arm Cortex M

الدرس ٩ Arm Cortex M4 Nested Vectored Interrupt Controller Nvic Youtube

Nested Vector Interrup Sjsu Cmpe Embedded Courses

What Is Nested Vector Interrupt Control Nvic Microdigisoft Com

Vectored Interrupt Controller And Nested Vectored Interrupt Controller

What Is Nested Vector Interrupt Control Nvic

Vectored Interrupt Controller And Nested Vectored Interrupt Controller

0 comments

Post a Comment